The PCI SIG has penned a blog post with an update on its progress in drafting the PCIe 6.0 specification. It only completed the PCIe 5.0 spec back at the end of May this year, but was very quick off the blocks to outline the PCIe 6.0 spec, and its target doubling of raw bit rate to 64GT/s. Now it has announced that revision 0.3 of the PCIe 6.0 specification is complete, and it plans to have the final specification available for 2021.

The announcement that the PCI SIG has reached revision 0.3 of the PCIe 6.0 specification is rather light on technical details. It reiterates the information we had back in June, that the technology will "double the data rate to 64GT/s while maintaining backward compatibility with all previous spec generation." Furthermore, PCIe 6.0 "includes PAM-4 (Pulse Amplitude Modulation with 4 levels) encoding and low-latency Forward Error Correction (FEC) with additional mechanisms to improve bandwidth efficiency," relays the blog post.

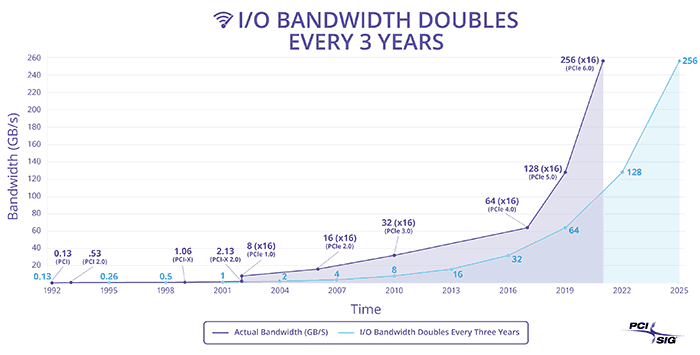

For some background info, the 64GT/s figure refers to GigaTransfers per second over the interface. That equates to roughly 256GB/s of bandwidth (or 128GB/s in each direction), as you can see in the official PCIe standard comparison graph, reproduced above. The above graph also demonstrates that the PCI SIG intends to keep pressure on the standard's development and not leave a big gap between revisions, as witnessed with the transition from PCIe 3.0 to PCIe 4.0.

2021 isn't very soon, considering that the PCI SIG and its working group of 800 industry-leading member companies appear to have got almost a third of the way there in just a few months. However, we can't expect such a development, consultation and coordination process to be perfectly linear.