The PCI Special Interest Group (PCI-SIG) has announced a milestone in the development of the PCIe 6.0 specification. It has just confirmed that the specification is now at version 0.7, and related documentation has been distributed to members. Key features of the PCIe 6.0 specification are its doubling of data rates compared to PCIe 5.0, to 64 GT/s speeds, its move to PAM4 encoding, the introduction of low latency FEC, and of course backwards compatibility with all previous specification versions.

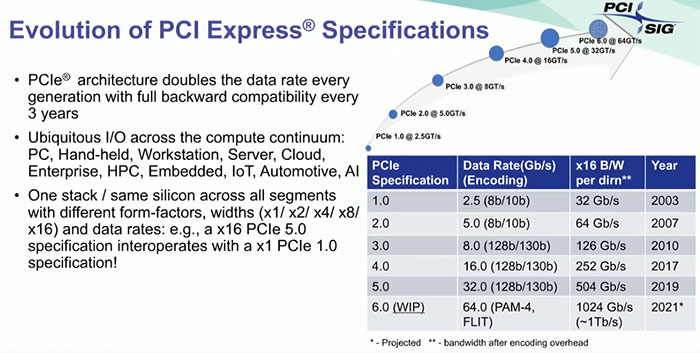

In its blog post about the update the PCI-SIG was pleased with the progress which it had made even with the restrictions imposed upon its members due to the current pandemic. Over recent years the organisation has been speeding up its timeline for new version introductions. PCIe 3.0 was released back in 2010, with a long wait before PCIe 4.0 was finalised in 2017 - and this is only now becoming mainstream. PCIe 5.0 was finalised in 2019 and PCIe 6.0 is on track for being finalised in 2021.

Official highlights of PCIe 6.0 are as follows:

- A data rate of 64 GT/s speeds, doubling the 32GT/s data rate of the PCIe 5.0 specification

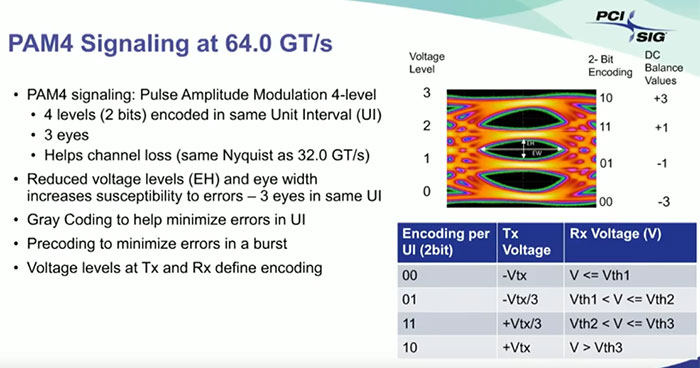

- A move to PAM4 (Pulse Amplitude Modulation with 4 levels) encoding

- Low-latency Forward Error Correction (FEC) with additional mechanisms to improve bandwidth efficiency

- Backwards compatibility with all previous specification generations

The doubling of data rate is well established on previous roadmaps so isn't a surprise to see. PAM4 encoding is said to reduce channel loss by running at half the frequency with two bits per Unit Interval. For more info on PAM4 you can check out the blog post by Debendra Das Sharma, PCI-SIG Board Member and Intel Fellow.

Das Sharma has also blogged about another highlighted feature of PCIe 6.0, error detection and correction with FEC. FEC is an abbreviation of Forward Error Correction and it works in tandem with Cyclic Redundancy Check (CRC) in PCIe 6.0.

With PCIe 6.0 finalised sometime in 2021 one shouldn't expect devices on the market utilising the standard until 2023 or onwards.