When we think of embedded processors today, we think of ARM and only ARM, however, not too long ago, it was processors and instruction sets designed by MIPS that were to be found in embedded devices, such as set-top boxes, routers and robots, with the original PlayStation, PSP and Nintendo 64 all based on a MIPS design; even the PlayStation 2 featured the MIPS instruction set.

Looking to retake some of the territory stolen from it by ARM and to fight for territory always held by ARM, MIPS has launched its new 'Aptive' range of cores, improving chip performance by 50 per cent with no increase in power consumption.

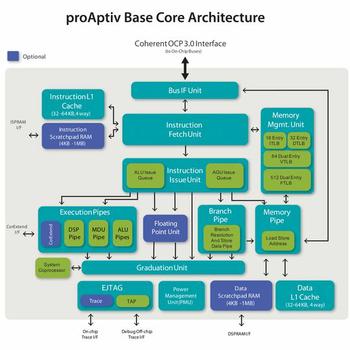

To place this into perspective, MIPS's most powerful Aptiv member is 'proAptiv', which can be configured from one to six cores. The design occupies roughly half the space of ARM's Cortex-A15 and so SoC designers can fit four cores into the space of a comparable dual-core Cortex-A15 design or, alternatively, a level 2 cache. At 1GHz, a quad-core variant achieves 14,000 DMIPS, a result comparable again, to the Cortex-A15, however MIPS claims superior real-world performance through Coremark benchmarking, achieving its performance with a shorter pipeline, better able to cope with unpredicted branching. proAptiv will initially be offered at speeds of up to 1.5GHz.

Other members of the Aptiv family are the 'interAptiv', topping out at 1GHz, suitable for low-power roles and the 500MHz 'microAptiv', for highly-embedded single core designs.

MIPS's announcement may seem like a lost cry in the wind against the storm that is ARM, however the firm has already gained full support from the Android NDK and has confirmed it has signed up several clients. Being able to cram four cores into the same space as a dual-core ARM Cortex-A15 whilst achieving the same DMIP performance and even greater Coremark performance indeed gives this new design a competitive edge.