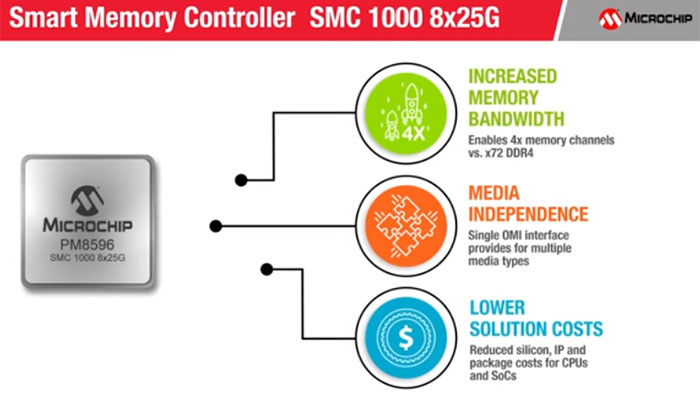

Arizona-based embedded control solutions company Microchip Technology Inc., a leading provider of microcontroller, analogue, FPGA, connectivity and power management semiconductors, has entered the memory infrastructure market. Its pioneering product is the SMC 1000 8x25G serial memory controller for high-performance data centre computing. The headlining quality of the SMC 1000 8x25G is that it enables high memory bandwidth required by next-generation CPUs and SoCs - up to 4x bandwidth - to alleviate the bandwidth bottleneck between CPU and RAM, with obvious benefits for AI and machine learning.

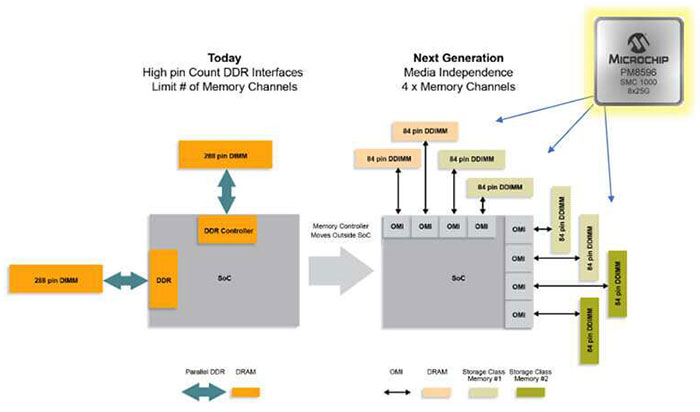

Microchip's serial memory controller is designed to address the gap that has opened up between the advance in CPU processor core counts and the average memory bandwidth available. "As the number of processing cores within CPUs has risen, the average memory bandwidth available to each processing core has decreased because CPU and SoC devices cannot scale the number of parallel DDR interfaces on a single chip to meet the needs of the increasing core count," asserts the tech firm.

To address the above concerns, Microchip's SMC 1000 8x25G interfaces to the CPU via 8-bit Open Memory Interface (OMI)-compliant 25Gbps lanes and bridges to memory via a 72-bit DDR4 3200 interface. It explains that "the result is a significant reduction in the required number of host CPU or SoC pins per DDR4 memory channel, allowing for more memory channels and increasing the memory bandwidth available." In promoting its SMC 1000 8x25G, Microchip makes the case for OMI support which unlocks the memory protocol type/rate support with its media-independent OMI interface.

Perhaps you haven't heard of Microchip before, but it is partnered by some semiconductor tech giants. IBM, for example has partnered with Microchip to enable the strategic decision for POWER processor memory interfaces to utilise OMI standard interfaces for increased bandwidth. AMD and Google are also championing the OMI standard. Moreover, SMART Modular, Micron and Samsung Electronics are building multiple pin-efficient 84-pin DDIMMs with capacities ranging from 16GB to 256GB, conforming to the draft JEDEC DDR5 standard DDIMM form factor - and leveraging the SMC 1000 8x25G.

Source: Microchip press release, via EE Times.