Synopsys has readied the world's first complete solution for PCI Express 6.0 technology. Its solution includes hardware/firmware/software to address the controller, PHY (physical layer, usually an integrated circuit) and verification IP. This significant step for the industry will enable early development of PCIe 6.0 SoC designs to address the evolving latency, bandwidth and power-efficiency requirements of computing segments like HPC, AI and storage.

The new DesignWare IP for PCIe 6.0 is said to be built on Synopsis' widely deployed and silicon-proven previous version, embracing the latest features of the standard. With PCIe 6.0 users can expect:

- A low-latency controller with new MultiStream architecture delivers up to 2X the throughput of the PCIe 5.0 specification.

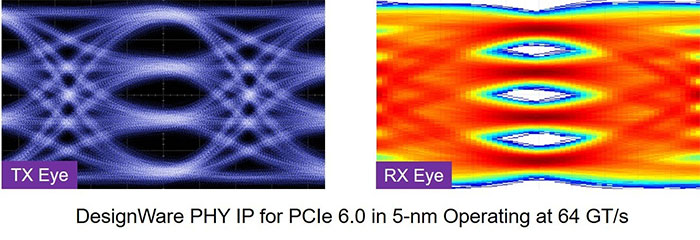

- A high-performance PHY produced on the 5nm process, with unique analogue and DSP techniques which can provide 20 per cent lower power across chip-to-chip, riser card and backplane interfaces.

- The latest features of the spec such as 64GT/s PAM4 signalling, FLIT mode, and L0p power state.

Synopsis provided a few more details about the PHY. It says this 5nm component has a 1024-bit architecture, allowing designers to achieve 64GT/s x16 bandwidth at 1GHz. The PHY is ready for accelerated test bench development with built-in verification plan, sequences and functional coverage thanks to its native SystemVerilog/UVM architecture. Furthermore, it is said to include unique adaptive DSP algorithms that optimise analogue and digital equalization to maximize power efficiency, with near zero downtime. Using a placement-aware architecture of the DesignWare PHY IP for PCIe 6.0 minimises package crosstalk and allows dense SoC integration for x16 links, adds Synopsys.

Verification IP for PCIe 6.0 is available now. The DesignWare Controller and PHY IP for PCIe 6.0 early access are scheduled to be available in Q3 2021.

The PCI-SIG released the PCIe 6.0 spec v0.7 back in November last year. HEXUS reported upon this and the major change to PAM4 encoding (Pulse Amplitude Modulation with 4 levels) at the time.