Roughly within a year AMD plans to launch its fourth gen Epyc processors (Genoa), according to official roadmaps shared previously. AMD has yet to release the third gen Epyc processors (Milan), but did take time out at CES in January to provide a demo of a 2P system easily trouncing a contemporary Intel system in WRF – a popular climate modelling app.

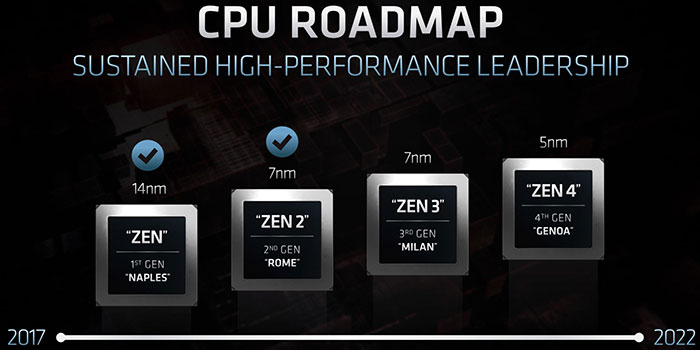

So what advances are going to be delivered by Genoa? As you can see above the official roadmap shows that Genoa will move to utilising AMD's Zen 4 processor cores, and it will be fabricated at 5nm. These are the major changes it has shared regarding its continuous improvement of its server platform. Of course there is more to it that this, and Twitter's ExecutableFix reckons he has added quite a lot of meat to the bones that we are certain of.

Key features of Genoa include the following according to the Twitter source:

- 96-cores (192 threads)

- 12-channel DDR5-5200

- 128 PCIe gen 5.0 lanes (160 for 2P systems)

- 320W TDP (configurable TDP to 400W)

- SP5 (LGA-6096) socket

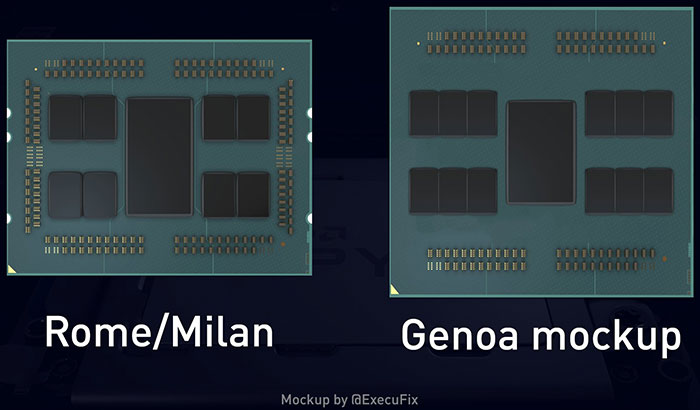

The above specs list was added to with a to-scale mock up of Genoa based upon the Rome processor. You can see that SP5 is squarer than its predecessor, and it should have 2002 extra pins compared to the current gen Epyc processors (LGA-4094). In the image below you can see the central I/O die is flanked by 12 chiplets, rather than eight, and this is how AMD expands the core count with Genoa. With each chiplet capable of packing eight Zen 4 cores that means the max core count of a Genoa processor will be 96C/192T.

Speaking of major changes, it is thought that the memory bus width will be 50 per cent wider and serviced by the 12-channel DDR5 memory interface, supporting DDR5-5333. PCIe gen 5.0 will double the bandwidth over the current PCIe gen 4.0. Last but not least, AMD is expected to be upgrading the I/O die to a newer process tech (possible 7nm) to rein in its size and improve its efficiency.

Genoa should be revealed / demoed at CES 2022 and released a year after Milan turns up. It is expected to compete against the Intel Xeon Sapphire Rapids architecture which similarly features DDR5 and PCIe gen 5.0 support.

Update: A purported AMD Eypc Genoa slide that surfaced on ChipHell says that the Zen 4 cores which will feature in this processor supports AVX3-512 and BFLOAT16 instructions. As always, sprinkle some salt on info from these sources.

Sources: ExecutableFix, VideoCardz (2), TechPowerUp