We keep a close eye on the AMD vs Intel battle if the fields of desktop PCs and performance / gaming laptops, but there is another intense battle going on in the more generalist laptop market where low-power thin and light designs are popular for portability and great battery life. In this market Intel's Tiger Lake-U processors look set to be popular, offering a good balance of performance and low power usage (7.5W to 18W TDP envelope). However, it may about to face tough competition with the introduction of AMD Van Gogh.

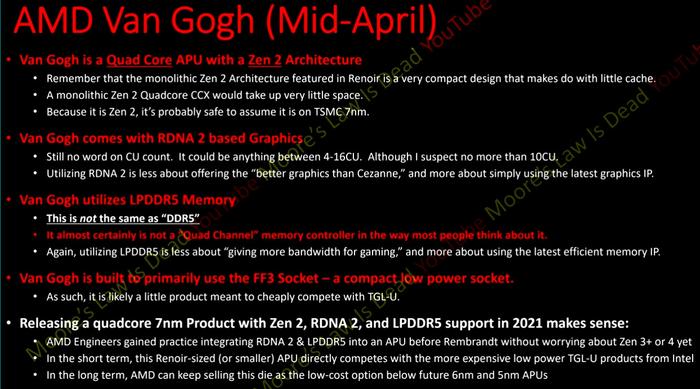

Moore's Law Is Dead (MLID) took to YouTube just ahead of the weekend to provide a sketch of the key specs of AMD Van Gogh APU and its capabilities from various sources including his own. The key bullet point slide about AMD's unannounced mobile APU is reproduced below for your convenience. Remember, these are just rumours for now.

Click to zoom image

In a brief summary of the above and what is talked about during the video, MLID says that the AMD Van Gogh APU will be a design with a 4C/8T Zen 2 core configuration, with approx 10 RNDA 2 CUs, and LPDDR5 support, suing the FF3 socket. Design choices have been made to create a cheap, accessible, low power alternative to Intel Tiger Lake-U. It is thought that the 7nm Van Gogh APU will be able to be made and sold cheaply as higher-end IPs move onto TSMC N6 and N5 processes.

Towards the end of the video MLID told viewers that, while the Van Gogh APU is definitely a real product that has been designed by AMD, there is still a chance that it will not be released as a commercial product to systems makers. In other words, it is ready to go, but AMD needs to secure a certain level of interest in it, from systems making partners, or even one major partner in particular, before committing to make these APUs on the heavily burdened production lines at the likes of TSMC. One product type where MLID reckons the AMD Van Gogh would be a great choice is in a PSP/Switch format handheld gaming PC. Whether it ends up in shipping products or not, Van Gogh will have been a useful learning and development process for AMD engineers in preparing PC APUs with technologies like RDNA 2 and LPDDR5.