We have only mentioned HBM3 once before in the HEXUS news. The next gen high bandwidth memory technology was touched upon in presentations by Samsung and SK hynix at the Hot Chips Symposium last year. At that time we learned that HBM3 would improve on density, bandwidth, cost, and power consumption and it was hoped it would be widely welcomed by a range of industries from high performance computing and servers, to graphics, networking and many more.

Though no hard figures were projected last year, Samsung's HBM3 presentation did indicate that HBM3 density would be 2x or better, peak bandwidth would be 2x or better and IO/Core voltage would be "much less", compared to HBM2.

Now we have some more refined figures for HBM3 from Rambus. The data was shown to investors at a company event earlier this week. By all indications the release of HBM3 product is quite a way off so keep in mind that specs might change before this third gen HBM materialises.

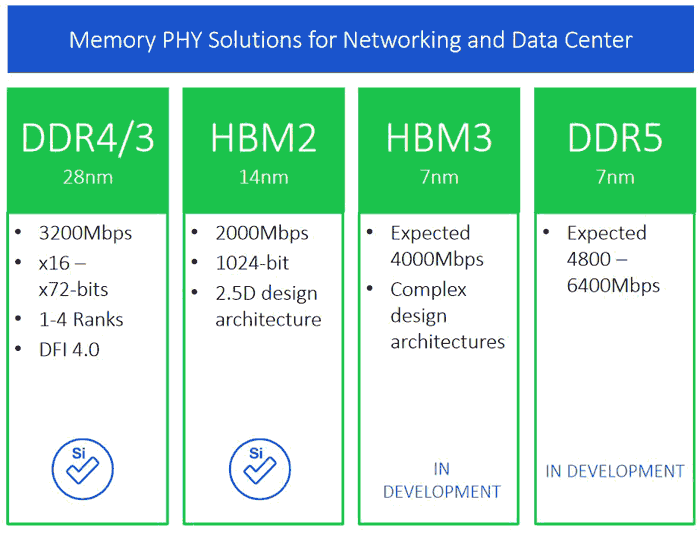

The key slide from the Rambus event is reproduced above, and came via ComputerBase. You can see that, as indicated a year back, the expected bandwidth of HBM3 is 4000Mbps. Rambus also signals that the design complexity goes up. HBM2 used a 2.5D architecture and with HBM3 the stack height is increased.

The only other data of note from the Rambus presentation slide is that HBM3 will be made on the 7nm node. It isn't expected that we will see 7nm semiconductor products until 2019 at the earliest.

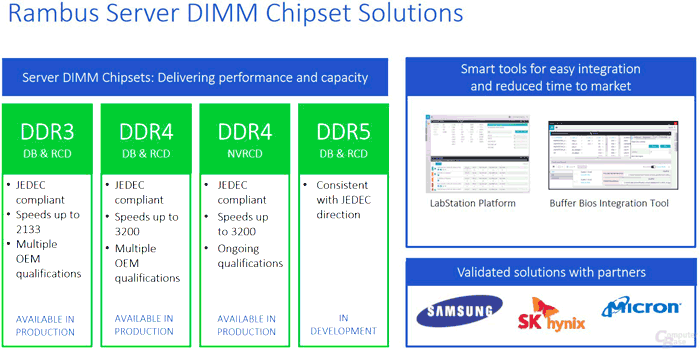

Rambus also mentioned DDR5 on two of its slides. In the first slide, sitting alongside the HBM3 in development box you can see DDR5 mentioned. The key info here is that DDR5 will deliver an expected bandwidth of 4800 - 6400Mbps. Like HBM3, it is set to be fabricated at 7nm.

For GDDR5, the new investor slide isn't very informative overall. Never mind, we got a much more detailed rundown of Rambus DDR5 technology back in September when it announced an industry first fully functional DDR5 DIMM prototype. Similar to HBM3's inter-generational advances, DDR5 is said to deliver double density, double bandwidth, and greater efficiency than its predecessor. At the time of that report it was estimated that DDR5 could reach the market by 2019.